CPU - නියෝග නල මාර්ග (Instruction pipeline)

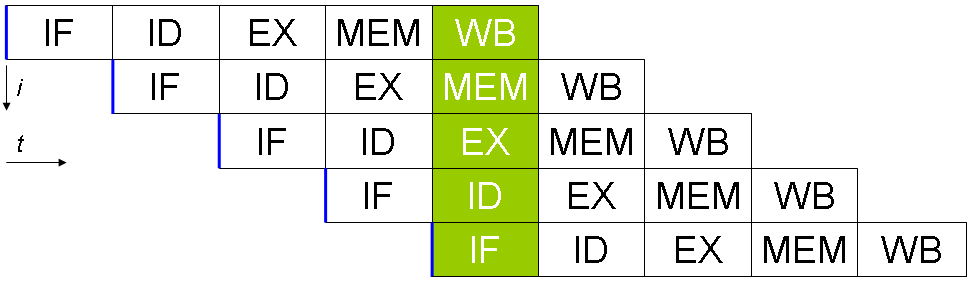

RISC යන්ත්රයක අදියර 5 කින් යුත් මූලික නල මාර්ග (1F = නියෝග ගෙන්වා ගැනීම , ID = නියෝග විකේතනය කිරීම , EX = ක්රියාත්මක කිරීම , MEM = මතක පිවිසුම , WB = රෙජිස්ටරය නැවත ලිවීම)

නියෝග නල මාර්ග යනු පරිගණක හා අනෙකුත් සංඛ්යාංක ඉලෙක්ට්රෝන උපකරණ සැළසුම් කිරීමේදී ඒවායේ නියෝග සංඛ්යාව (ඒකක කාලයකදී ක්රියාත්මක කරන නියෝග ගණන) වැඩි කිරීමේ තාක්ෂණික ක්රමයකි.

ඊළග රූප සටහනේ අදහස් කර ඇති පරිදි නල මාර්ගයක් සේ උපකල්පනය කරන්නේ එක් නියෝග (SISD) සංකල්පයක් ඇති විට , වැඩසටහෙන් අනුපිළිවෙලකට ඇති නියෝග ක්රියාත්මක කිරීමේදී ඒවා එකිනෙක අතිච්ඡාදනය වන බවයි. (සිරස ‘i' නියෝග , තිරස ‘t’ කාලය)

බොහෝමයක් නවීන cpu ක්රියාත්මක වන්නේ ස්පන්දකයක් මගිනි. cpu අභ්යන්තරිකව ලොජික් (logic) හා ෆ්ලිප් ෆ්ලොප් (flip flop) ඔවුන්ගේ නව අගයක් ගන්නා අතර ඉන්පසු එහි අඩංගු තර්කය අනුව (ලොජික්) නව අගයන් විකේතනය කිරීමට යම් කිසි කාලයක් ගනී. ඉන්පසු ඊළගට ස්පන්දනක සංඥාව පැමිණෙන අතර ෆිලිප් ෆ්ලොප් නැවත ඒවායේ අගයක් ගනී. මෙලෙස දිගින් දිගටම සිදුවෙයි. ලොජික් නැවත ඒවායේ අගයක් ගනී. මෙලෙස දිගින් දිගටම සිදුවෙයි. ලොජික් කුඩා කොටස්වලට කඩා එම කොටස අතරට ෆ්ලිප් ෆ්ලොප් ඇතුළත් කිරිමෙන් ලොජික් වලංගු ප්රතිදාන දීමට ගතවන කාලය අඩු කරගත හැක. මෙමගින් ස්පන්දක ආවර්තය අඩු කර ගත හැක. උදාහරණයක් ලෙස RISC ප්රවාහය අදියර 5කට බෙදා ඇති අතර එක් එක් කොටසක් අතර ෆ්ලිප් ෆ්ලොප් කාණ්ඩ ඇත.

1. නියෝග ගෙන්වා ගැනීම 2. නියෝග විකේතනය හා රෙජිස්ටරය ගෙන්වා ගැනීම 3. ක්රියාත්මක කිරීම 4. මතක පිවිසුම 5. රෙජිස්ටරය නැවත ලිවීම

උපද්රව : ක්රමලේඛ කරුවන් එකලස් කිරීමේ කේත (Assembly Code) ලිවීමේදී සෑම නියෝගක්ම මීළඟ නියෝගය ක්රියාත්මක වීමට පෙර ක්රියාත්මක වන බවට උපකල්පනය කරයි. මෙම උපකල්පනය නල මාර්ග මගින් අහෝසිකර දමයි. මේ නිසා ක්රමලේඛයක් වැරදියට හැසිරීමේ තත්වය උපද්රවයක් ලෙස හඳුන්වනු ලැබේ. උපද්රව වළක්වා ගැනීම සඳහා ෆෝවර්ඩින් හා ස්ටෝලින් (Forwarding and Stalling) වැනි තාක්ෂණික ක්රම භාවිතයේ ඇත.

නල මාර්ග නොවන ක්රමයක් භාවිතය අකාර්යක්ෂම වේ. මන්ද, නියෝග චක්රය අතරතුර සමහරක් CPU මොඩියුල අක්රීයව තිබියදී වෙනත් මොඩියුලයක් ක්රියාකාරී වේ. නල මාර්ග මගින් CPU වල අක්රීය කාලය සම්පූර්ණයෙන් නැති නොකළත් එම මොඩියුල සාමාන්තරව වැඩ කරවීමට සැළැස්වීමෙන් ක්රමලේඛ ක්රියත්මක කිරීම සැළකිය යුතු ලෙස වැඩි කරයි.

ප්රධාන නල මාර්ග පිහිටුවා ඇති සකසූ (processors) අභ්යන්තරිකව එකිනෙකට වෙනස් ක්රියාත්මක අර්ධ ස්වාධීනව වැඩ කළ හැකි අදියර දෙකකට සැලසුම් කර ඇත. එක් එක් අදියර සැලසුම් කර දාමයකට සම්බන්ධ කර ඇත. එම නිසා එක් එක් අදියරෙහි ප්රතිදානය අනෙක් අදියරේ ආදානය ලෙස ඇතුල් වේ. මෙලෙස සකසුව සංවිධානය කිරීමෙන් මුළු සකසූ කාලය සැළකිය යුතු ලෙස අඩුවේ.

අවාසනාවකට මෙන් සියලු නියෝග ස්වාධීන නොවේ. සරල නල මාර්ගයකදී නියෝගයක් ක්රියාත්මක වීමට අදියර 5ක් අවශ්ය වේ. සම්පූර්ණ කාර්ය සාධනයෙන් යුතුව වැඩ කිරීමට පළමුවැන්න සම්පූර්ණ වන අතරතුර අපර ස්වාධීන නියෝග හතරක් ක්රියාත්මක කළ යුතුවේ. පළමු නියෝගයේ ප්රතිදානය මත නොයැපෙන නියෝග හතරක් නොමැති නම් , එය විසඳන තෙක් නල මාර්ග පාලක තර්කය ස්ටෝල් හෝ නිශ්ඵල ස්පන්දක චක්ර නල මාර්ගය තුළට ඇතුල් කළ යුතුය. වාසනාවකට මෙන් “ස්ටෝලින්” අවශ්ය ගැටළු නැවත යොමු කිරීම (Forwarding) මගින් සැළකිය යුතු ප්රමාණයකට විසඳා ගත යුතුව තිබේ.